僕の最新プロジェクトのひとつがBaochip-1xだ。これはTSMC 22nmプロセスで製造された「ほとんどオープンな」フルカスタムシリコンチップで、高信頼性(high assurance)アプリケーションを対象としている。セキュリティチップではあるが、他のどのセキュリティチップよりもはるかにオープンだ。また、Raspberry Pi RP2350(Pi Pico 2に搭載)とNXP iMXRT1062(Teensy 4.1に搭載)の間を埋める、汎用マイクロコントローラとしての側面も持っている。

このプロジェクトはBetrustedイニシアチブの最新の一歩であり、8年前にエド・スノーデンと共に「国家レベルの敵対者による大量監視という文脈において、ぼくらはハードウェアが私たちを裏切らないと信頼できるのか」という問いに答えようとした作業から生まれた。Baochip-1xのCPUコアは、僕が作ったセキュリティデバイスPrecursorの内部で使用されていたFPGA SoCから直接派生している。また、僕が開発を支援した純Rust製の組み込みOSであるXousを実行するために明示的に設計されており、シリコンの正しい構築を非破壊で検査するために僕が先駆けて開発した手法であるIRIS検査との互換性も意図的に持たせている。

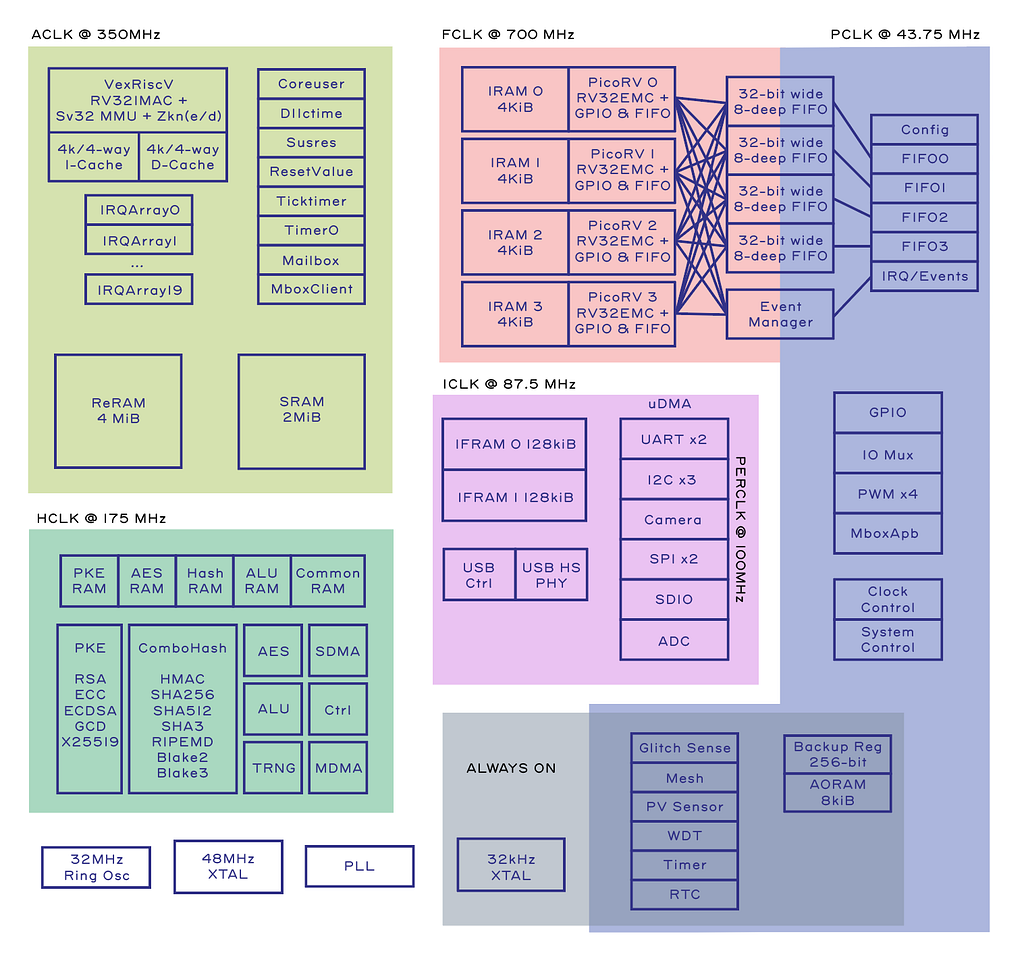

簡単に言えば、Baochip-1xは、350MHz Vexriscv CPU+MMUを搭載し、4つの700MHz PicoRV32を備えたI/Oプロセッサ(「BIO」)、4MiBの不揮発性メモリ(RRAM形式)、および2MiBのSRAMを組み合わせたSoCだ。さらに、TRNG(真性乱数生成器)、各種暗号アクセラレータ、セキュアメッシュ、グリッチ検出器、ECC保護RAM、ハードウェア保護されたキースロット、単方向カウンタなど、通常はセキュアエレメントにのみ搭載される機能もこのチップに詰め込まれている。

このチップは、専用のマスクセットを使用して、完全に量産認定されたTSMCプロセスで製造されている。つまり、これは限定生産のMPW(マルチプロジェクトウェハー)による試作品ではない。Baochipのサプライチェーンは、もし需要があれば数百万個のチップを生産できる能力を持っている。

このチップは、専用のマスクセットを使用して、完全に量産認定されたTSMCプロセスで製造されている。つまり、これは限定生産のMPW(マルチプロジェクトウェハー)による「お試し」チップではない。Baochipのサプライチェーンは、そのような需要が現れれば数百万個のチップを生産できる能力を持っているのだ。高信頼性ソフトウェアを実行するために構築されたハードウェアBaochip-1xの重要な差別化要素は、メモリ管理ユニット(MMU)を搭載していることだ。僕の知る限り、この性能・統合度のクラスのマイクロコントローラでMMUを搭載しているものは他にない。OS専門用語に詳しくない方のために説明すると、MMUは、スマートフォンやデスクトップで動作するソフトウェアと、トースターで動作するソフトウェアを分けているものだ。MMUは各アプリケーションを独自の仮想メモリ空間に配置することで、安全でロード可能なアプリケーションを実現する。

MMUは1960年代にまで遡る由緒ある技術だ。ページベースのメモリ保護方式は十分に理解されており、時の試練に耐えてきた。僕はその原理を何百人もの学部生に教えてきたが、今なお現代のOSの基盤であり続けている。

(上記:Kilburnらの論文「One-level storage system」(IRE Transactions, EC-11(2):223–235, 1962)に示された初期の仮想メモリ方式の図)セキュリティ指向の機能を評価する際、古いことが必ずしも悪いわけではない。むしろ、時の試練に耐えていることは肯定的なシグナルだ。例えば、AES暗号は約26年前に登場した。コンピュータ技術としては古く思えるかもしれないが、多くの暗号研究者は、何年にもわたって各国の代表を含む何百人もの暗号研究者が解読を試みてきたという実績があるからこそ、新しい暗号よりもAESを推奨している。

僕はCHERI、PMP、MPUといった新しいメモリ保護技術についても知っている。技術者として、こういった技術について考えるのは大好きだ。実際、僕の博士論文では、新しいCPUアーキテクチャにおけるCHERI型のハードウェア機能とタグ付きポインタの使用を提唱した。

しかし、実践的なシステムアーキテクトとして、MMUをこれらに取って代わられるべきものと見なす理由はない。実際、MMUはこれらすべてのプリミティブと組み合わせることが可能だ。同じRISC-V CPUにPMPとMMUの両方を搭載することは有効だ。また、CHERIのような技術をポインタのハードウェアによる境界チェックに使用していたとしても、それだけでは透過的なアドレス空間の再配置は実現できない。ページベースの仮想メモリがなければ、各プログラムはコンパイル時に物理アドレス空間の重複しない領域にリンクする必要があり、スワップメモリを使用することもできない。

ここで疑問が生じる:MMUがそれほど明らかに良い追加機能であるなら、なぜもっと普及していないのか?そんなに明白な選択なら、なぜもっと多くの企業が自社のチップに搭載しないのか?

組み込みSoCに見られるような「小型」CPUは、その誕生以来ずっとこの機能を欠いてきた。この慣習は、1990年代にARM7TDMIコアが登場したことにまで遡ると考えられる。当時、トランジスタは貴重であり、メモリはさらに貴重だった。そのため、ページテーブルを保持するだけの容量さえもない数キロバイトのRAMしか持たないデバイスにとって、仮想メモリは製品と市場の適合性が高いものではなかった。ARM7TDMIコアの効率性と低コストは大成功を収め、10億個以上が出荷され、ARMを組み込みSoC分野の支配的プレーヤーとして確立した。

それから30年が経ち、ムーアの法則は私たちに数万倍もの能力をもたらした。今日では、小指の爪よりも小さいシリコンの一片に、1990年代のフルサイズのPCデスクトップよりも多くのトランジスタが詰まっている。この進歩にもかかわらず、これらの小さなシリコンの一片は、1990年代に確立されたパターンに従い続けている。小型システムは、アドレス分離のないフラットなメモリ空間を持つ、というパターンだ。

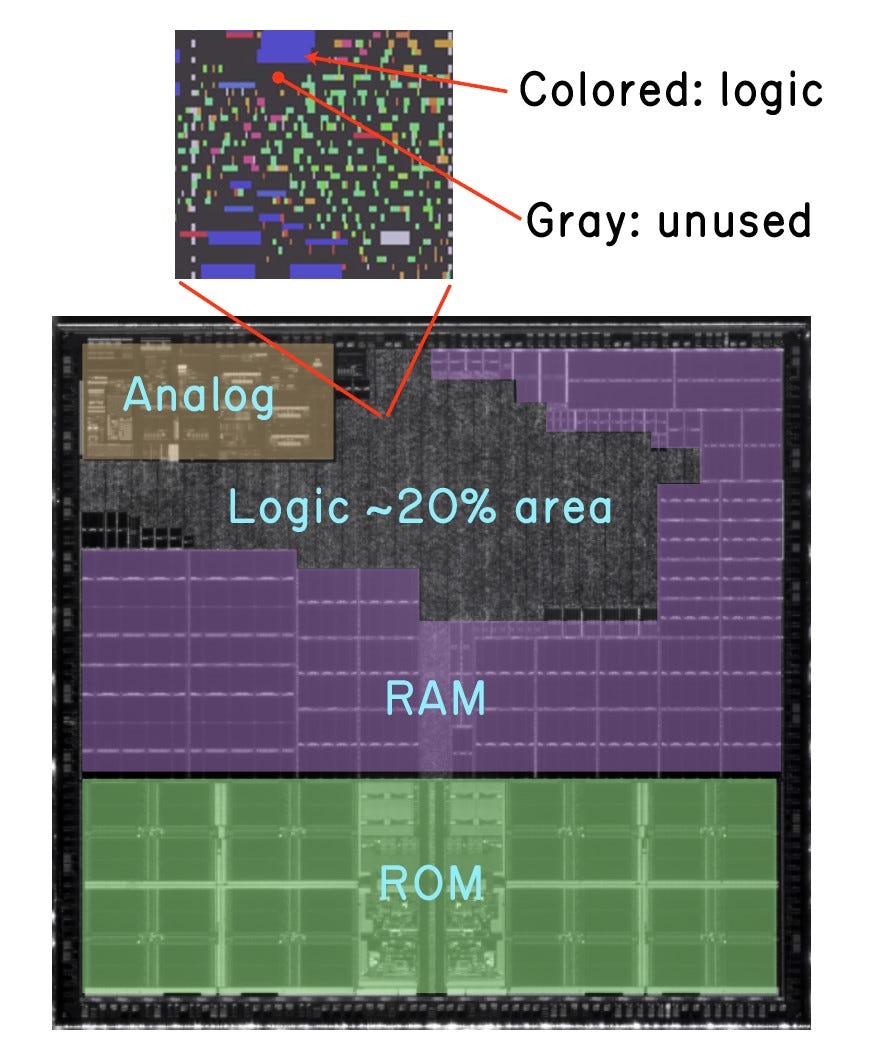

(上記:現代の22nm SoCのダイショット。このシリコンの一片は一辺約4mmで、1990年代のデスクトップPCよりも多くのトランジスタを含んでいる。ロジック領域が、シリコン面積の観点ではアクティブゲートよりも空きスペースが多いことに注目してほしい。)根本的な原因は、MMUがあまりにも価値が高いからであることがわかる。MMUがなければ、Linux、BSD、Machを実行することはできない。そこでARMがIPポートフォリオをAシリーズ、Rシリーズ、Mシリーズに分割した際、低コストのMシリーズコアには、高級なAシリーズコアの価格侵食を防ぐために、MMUの搭載が禁止された。その代わりに「MPU」として知られる独自仕様のハックが導入され、ある程度のメモリセキュリティが提供されたが、スワップメモリやアドレス空間の再配置といった利点への簡単な道筋はなかった。

僕らはこの慣習に長く縛られすぎて、その前提に疑問を投げかけることを忘れてしまっていたのだ。

RISC-Vのようなオープンなアーキテクチャ仕様と、VexriscvのようなRISC-V仕様の完全にオープンな実装のおかげで、私は「何をSoCに搭載してよくて何がダメか」という誰かのルールに縛られることはない。だから、僕は自由に、Baochip-1xにMMUを搭載するという選択をすることができた。

これにより当然、愛好家たちはBaochip-1x上でLinuxを動かそうと試みることができるようになるが、僕ら(主にSean “xobs” Crossとぼく)はすでに「Xous」と呼ばれる純Rust製のOSを書いている。これはMMUを組み込みながらも、Baochip-1xのような小容量メモリのデバイスを明確にターゲットとしたフレームワークだ。Xousの詳細はこの投稿の範囲を超えるが、興味があれば39C3で行った講演をご覧いただきたい。「今」こそ、よりオープンなフレームワークを選ぶべき時これは、「なぜ『ほとんどオープンなRTL』のSoCがこの時代に適切なのか」という核心的な議論につながる。オープンソース技術の断固たる支持者として、僕はファブから上まで完全にオープンなシリコンスタックが実現することを切望している。この問題の解決に取り組む複数のイニシアチブがあることに心強く思っているが、これは難しい問題だ。経済的に競争力のあるSoCを市場に投入できるほど堅牢なオープンソースシリコンエコシステムが整うまでには、10年以上かかる可能性があると見積もっている。

今日、組み込み製品を作ろうとしている人々にとって、残された実用的な選択肢はひとつだけだ。Cortex-M ARMデバイスを使い続けること、そしてハードウェアによるメモリ保護が必要な場合は、ソフトウェアを彼らの独自仕様のMPUに合わせて調整することだ。これは、僕らのコードベースをさらに独自仕様の標準に深く埋め込むことを意味する。本当に僕は、XousをARMの独自仕様のメモリ保護方式に移植することに時間を費やしたいのだろうか?もちろん答えはノーだ。

だからこそ、僕は、完全にオープンソースなPDK(プロセスデザインキット)が登場するのを待つ余裕はまったくないと主張する。完全にオープンな完璧なソリューションを待つよりも、今日、部分的にオープンなRTLのテープアウトを行う機会を得ることの利点は、僕には明確に理解できる。

今日利用可能な部分的にオープンなSoCは、ハードウェアの専門家でない人々も含め、オープンソースの未来に関心を持つより広範なコミュニティにとって力となる。より大きなコミュニティとして、僕らはARMからの依存脱却のプロセスを共に開始することができる。そうすれば、経済的に実現可能な「真にオープンな」シリコンの代替品が市場に登場したとき、それらは成熟したアプリケーションスタックに直接組み込むことができる。何しろ、シリコンへの需要を生み出すのはソフトウェアであって、その逆ではないからだ。

良いニュースとしては、Baochip-1xでは、データに対して「計算」を行うことができるものはすべて、シミュレーションと検査が可能であり、すでにGitHubで公開されている。クローズドソースとなっている部分は、AXIバスフレームワーク、USB PHY、PLL、電圧レギュレータ、I/Oパッドなどのアナログコンポーネントだ。

したがって、Baochip-1x SoCの特定の部分はクローズドソースだが、それらのいずれもデータの変換に関与していない。言い換えれば、クローズドソースのコンポーネントはすべて実質的に「配線」だ。一方から入ったデータは、もう一方から出てくるデータと一致するはずだ。これは「絶対的な信頼」という観点からは不満が残る(ブラックボックスである配線内のバックドアの可能性を完全に排除することはできない)。しかし、その境界を検査し、広範な可能性に対して正しく動作することを確認することは可能だ。完全な透明性ではないが、現在秘密情報の処理に使用している完全にNDAで囲まれたSoCよりもはるかに優れており、さらに重要なことに、オープンアーキテクチャ向けのコードを書き始めることができ、最終的には完全にオープンなシリコンからソフトウェアへの未来への道を切り開くことができる。ヒッチハイクで勝利を掴む半導体に詳しい方ならお気づきかもしれないが、このようなチップを製造するのは決して安くはない。にもかかわらず、僕はベンチャーキャピタルから1ドルも調達していない。また、僕は一人でこれができるような富裕層でもない。では、どうしてこれが可能なのか?

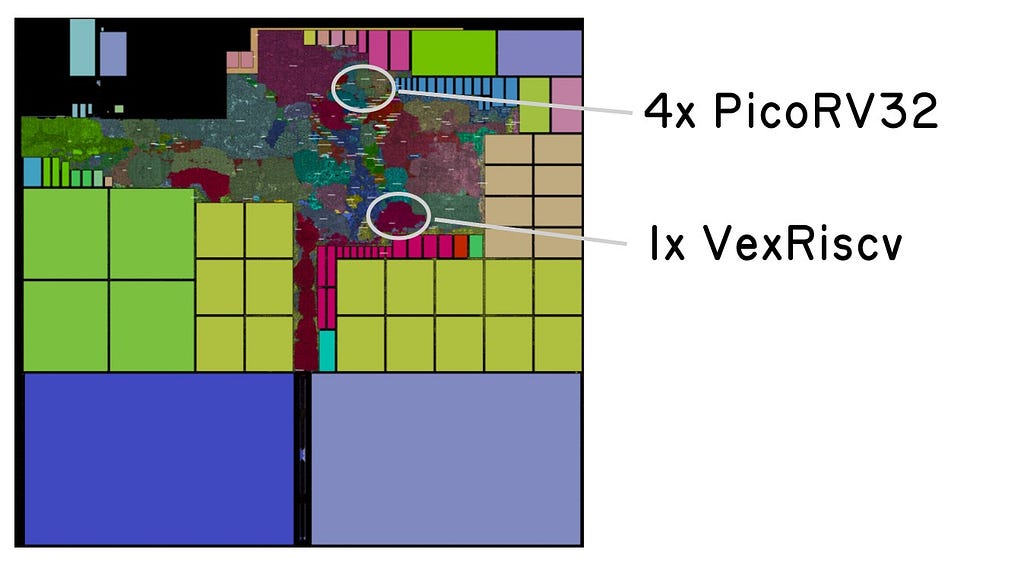

簡単に言えば、僕はCrossbar, Inc.が主に設計した22nmチップに「ヒッチハイク」したのだ。彼らが設計しているチップのフロアプラン上の未使用スペースに、僕が選択したCPUといくつかの追加機能を組み込むことができた。どのCPUをアクティブにするかを切り替えることで、実質的に1セットのマスク代で2つのチップを得ることができる。

上記:Baochipのフロアプラン。5つのオープンソースCPUコアの位置と相対的なサイズを示している。System-on-Chip(SoC)の内部を覗いたことのない方のために説明すると、現代のSoCのコストは主にペリフェラルとメモリによって決まる。CPU自体は面積のごく一部に過ぎず、Baochip-1xの場合もわずか数パーセントだ。さらに、すべてのペリフェラルは「メモリマップド」方式を採用しており、例えばLEDを点灯させる場合も、メモリ上の特定の場所にアクセスするだけで実現できる。

この「アクセス」を誰が行うかは重要ではない。ARMでもRISC-V CPUでも、あるいはステートマシンでも、ペリフェラルは同じように応答する。したがって、同じ「身体(ボディ)」に異なる「個性(パーソナリティ)」を与えることができる。つまりCPUコアを交換することで、同じ物理的なシリコン上で全く異なるコードベースを動作させることが可能になる。

長い答えは数年前に遡る。Crossbarは、いくつかの点で差別化された高性能なセキュアエンクレーブを構築したいと考えていた。特に、他のセキュリティチップと比較して比較的先進的な22nmプロセスで製造すること、そして不揮発性ストレージに自社のRRAM技術を使用することだ。RRAMはフラッシュメモリと同様に電源を切ってもデータを保持するが、書き込み時間が速く、ページサイズも小さく(32バイト)、40nm以下へのスケーリングが可能だ — — フラッシュがスケーリングできなくなった限界以下である。

プロセスの優位性を活かすことに加えて、Crossbarは設計について実用的なオープンソースであることで差別化したいと考えていた。セキュリティチップは、ユーザーからの透明性の要求にもかかわらず、伝統的にNDAの背後に包まれていたからだ。

逆説的だが、オープンソースのセキュリティチップは認証がより難しい。なぜなら、コモンクライテリアのような認証基準は、クローズドソースの欠陥をオープンソースの欠陥よりも「安全」と評価するからだ。私の理解では、その論理はおおよそ次のようなものだ。「ハッキングは難しいのだから、チップを悪用するための初期コストに少しでも障壁を加えられれば、チップ全体の実効的なセキュリティは向上する」。基本的に、セキュリティ評価を行うペネトレーションテスターが、ソースコードが公開されていればバグをより簡単に発見でき悪用できると判断した場合、ソースコードを共有することはスコアを下げることになる。その結果、オープンソースのチップの認証スコアは、クローズドソースのチップよりも悪くなる可能性が高い。そして、認証なしでは大口顧客にセキュリティチップを販売することはできないため、セキュリティチップは結局ほとんどがクローズドソースになってしまう。

なかなかクレイジーなシステムだと思わないか?しかし、大量のセキュリティチップを購入しているのが銀行や政府のような機関であり、そこにはリスク管理を主な関心事とする非技術系の管理者がいて、しかも技術的評価は外注しているということを考えれば、現状も少しは理解できる。銀行員がチップのソースコードをどうするというのだろう?

Crossbarはこの流れに逆らい、セキュリティチップにおけるオープンソースの透明性を求める声に応えたいと考え、私に戦略アドバイスを依頼してきた。私は彼らの支援に同意したが、ひとつ条件を付けた。私が選択したCPUコアを追加し、そのバージョンのチップを自分のブランドで販売することを許可することだ。理由のひとつは、Crossbarがリスク低減の観点から、独自仕様のARM CPUを採用したいと考えていたからだ。以前にチップ設計を経験した者として、テープアウト実績のあるコアを採用してリスクを低減したいという思いは理解できる。

しかし、オープンソース戦略アドバイザーとして、私はオープンソースを肯定的な機能と見なすユーザーは、少なくともCPUはオープンソースであることも期待するだろうと主張した。そこで私は、Precursor SoCから実績のあるVexriscv CPUコアをテープアウトに追加することを提案し、たとえ動作しなくてもそれを無効にすればチップの消費電力と面積の予算への影響は最小限に抑えられるという方法で実装することを約束した。

この取り決めからBaochip-1xは生まれた。Baochip-1xの市場投入これを書いている時点で、Baochip-1xの設計を含むウェハーは製造されており、数百個のチップが初期サンプリングプログラムを通じて配布されている。これらのエンジニアリングサンプルはすべて、僕が手作業でスクリーニングした。

しかし、それはまもなく変わる。現在、台湾新竹のファブで一群のウェハーが処理されており、そのうちの2枚は完全に量産認定されたBaochip-1xシリコンとして割り当てられる予定だ。これらは完全に自動化されたスクリーニングフローを経ることになる。このプロセスが順調に完了すれば、数千個のBaochip-1xを販売できるようになる。年内にさらに多くのチップが計画されているが、資金制約、リスク軽減、そして白紙のシリコンから完全に組み立てられたデバイスになるまでにかかる膨大な時間が相まって、次の在庫は2026年後半までずれ込むことになる。

もしBaochip-1xとそのMMUを活用したRustベースのOS「Xous」をいち早く試してみたい方は、「Dabao」評価ボードを検討してみてほしい。限定数がCrowd Supplyで予約受付中だ。もしこれがクローズドソースのチップであれば、これはローンチパートナー向けのサンプリングまたはプレビュープログラムのようなものになるだろう — — 通常はNDAと、アクセスを管理するゲートキーパーが付きまとうものだ。Baochipにはそのようなものは一切ない。このキャンペーンを「友人・家族向け提供」と考えてほしい。サプライチェーンが完全に立ち上がり整理される前の、量産サイクルの最も早い段階で、開発者やハッカーたちがこのチップをいじる機会だ。

この記事は、Bunnie Huangのブログ記事Baochip-1x: A Mostly-Open, 22nm SoC for High Assurance Applicationsを、本人の許可を得て翻訳したもの。 Dabao Boardは、高須の勤務するスイッチサイエンスにて日本販売予定。 また、Dabao Chipの詳細についてDiscord(日本語チャネル含む)にてご意見募集中。